# LM3150 SIMPLE SWITCHER<sup>®</sup> CONTROLLER, 42V Synchronous Step-Down

# **General Description**

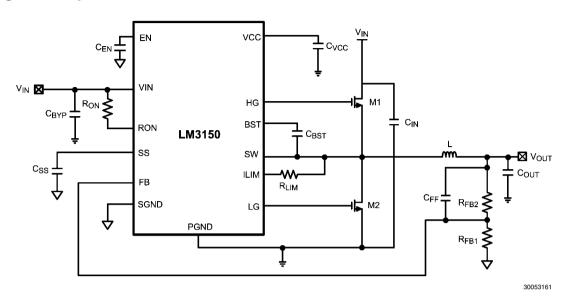

The LM3150 SIMPLE SWITCHER® Controller is an easy to use and simplified step down power controller capable of providing up to 12A of output current in a typical application. Operating with an input voltage range of 6V-42V, the LM3150 features an adjustable output voltage down to 0.6V. The switching frequency is adjustable up to 1 MHz and the synchronous architecture provides for highly efficient designs. The LM3150 controller employs a Constant On-Time (COT) architecture with a proprietary Emulated Ripple Mode (ERM) control that allows for the use of low ESR output capacitors, which reduces overall solution size and output voltage ripple. The Constant On-Time (COT) regulation architecture allows for fast transient response and requires no loop compensation, which reduces external component count and reduces design complexity.

Fault protection features such as thermal shutdown, undervoltage lockout, over-voltage protection, short-circuit protection, current limit, and output voltage pre-bias startup allow for a reliable and robust solution.

The LM3150 SIMPLE SWITCHER<sup>®</sup> concept provides for an easy to use complete design using a minimum number of external components and National's WEBENCH<sup>®</sup> online design tool. WEBENCH<sup>®</sup> provides design support for every step of the design process and includes features such as external component calculation with a new MOSFET selector, electrical simulation, thermal simulation, and Build-It boards for prototyping.

## **Features**

- PowerWise<sup>®</sup> step-down controller

- 6V to 42V Wide input voltage range

- Adjustable output voltage down to 0.6V

- Programmable switching frequency up to 1 MHz

- No loop compensation required

- Fully WEBENCH<sup>®</sup> enabled

- Low external component count

- Constant On-Time control

- Ultra-fast transient response

- Stable with low ESR capacitors

- Output voltage pre-bias startup

- Valley current limit

- Programmable soft-start

# **Typical Applications**

- Telecom

- Networking Equipment

- Routers

- Security Surveillance

- Power Modules

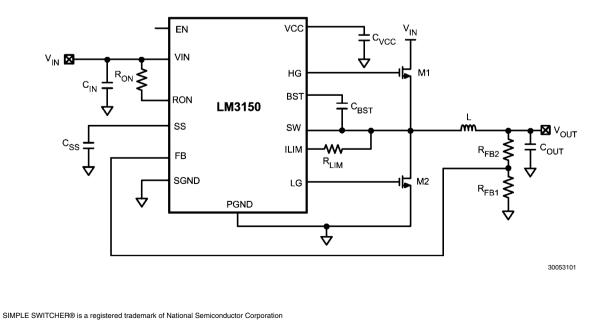

# **Typical Application**

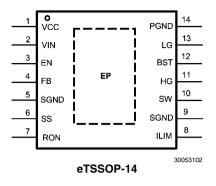

# **Connection Diagram**

# **Ordering Information**

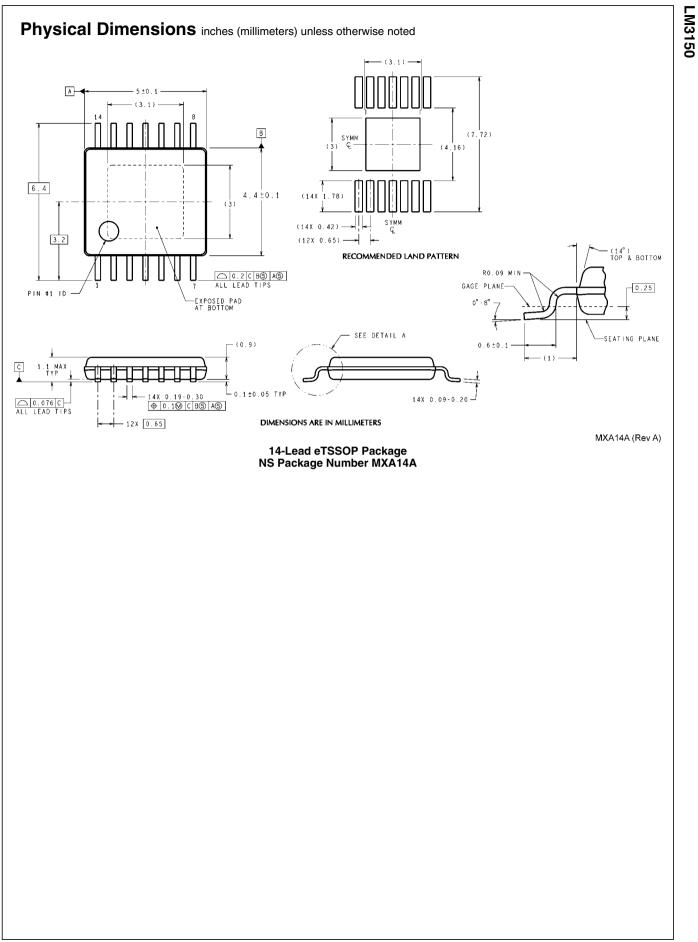

| Order Number | Package Type | NSC Package Drawing | Supplied As                   |

|--------------|--------------|---------------------|-------------------------------|

| LM3150MH     |              |                     | 94 Units per Anti-Static Tube |

| LM3150MHE    | eTSSOP-14    | MXA14A              | 250 Units in Tape and Reel    |

| LM3150MHX    |              |                     | 2500 Units in Tape and Reel   |

# **Pin Descriptions**

| Pin | Name | Description                           | Function                                                                                                                                                                                                                                                             |

|-----|------|---------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | VCC  | Supply Voltage for FET<br>Drivers     | Nominally regulated to 5.95V. Connect a 1.0 $\mu F$ to 2.2 $\mu F$ decoupling capacitor from this pin to ground.                                                                                                                                                     |

| 2   | VIN  | Input Supply Voltage                  | Supply pin to the device. Nominal input range is 6V to 42V.                                                                                                                                                                                                          |

| 3   | EN   | Enable                                | To enable the IC apply a logic high signal to this pin greater than 1.26V typical or leave floating. To disable the part, ground the EN pin.                                                                                                                         |

| 4   | FB   | Feedback                              | Internally connected to the regulation, over-voltage, and short-circuit comparators.<br>The regulation setting is 0.6V at this pin. Connect to feedback resistor divider between<br>the output and ground to set the output voltage.                                 |

| 5,9 | SGND | Signal Ground                         | Ground for all internal bias and reference circuitry. Should be connected to PGND at a single point.                                                                                                                                                                 |

| 6   | SS   | Soft-Start                            | An internal 7.7 $\mu$ A current source charges an external capacitor to provide the soft-start function.                                                                                                                                                             |

| 7   | RON  | On-time Control                       | An external resistor from VIN to this pin sets the high-side switch on-time.                                                                                                                                                                                         |

| 8   | ILIM | Current Limit                         | Monitors current through the low-side switch and triggers current limit operation if the inductor valley current exceeds a user defined value that is set by R <sub>LIM</sub> and the Sense current, I <sub>LIM-TH</sub> , sourced out of this pin during operation. |

| 10  | SW   | Switch Node                           | Switch pin of controller and high-gate driver lower supply rail. A boost capacitor is also connected between this pin and BST pin                                                                                                                                    |

| 11  | HG   | High-Side Gate Drive                  | Gate drive signal to the high-side NMOS switch. The high-side gate driver voltage is supplied by the differential voltage between the BST pin and SW pin.                                                                                                            |

| 12  | BST  | Connection for Bootstrap<br>Capacitor | High-gate driver upper supply rail. Connect a 0.33 $\mu$ F-0.47 $\mu$ F capacitor from SW pin to this pin. An internal diode charges the capacitor during the high-side switch off-time. Do not connect to an external supply rail.                                  |

| 13  | LG   | Low-Side Gate Drive                   | Gate drive signal to the low-side NMOS switch. The low-side gate driver voltage is supplied by VCC.                                                                                                                                                                  |

| 14  | PGND | Power Ground                          | Synchronous rectifier MOSFET source connection. Tie to power ground plane.<br>Should be tied to SGND at a single point.                                                                                                                                              |

| EP  | EP   | Exposed Pad                           | Exposed die attach pad should be connected directly to SGND. Also used to help dissipate heat out of the IC.                                                                                                                                                         |

# Absolute Maximum Ratings (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications. All Other Inputs to GND ESD Rating (Note 2) Storage Temperature Range -0.3V to 7V

-65°C to +150°C

2 kV

# Operating Ratings (Note 1)

| ).3V to 47V |

|-------------|

| -3V to 47V  |

| -0.3V to 7V |

| .3V to 52V  |

|             |

| V <sub>IN</sub>                    | 6V to 42V        |

|------------------------------------|------------------|

| Junction Temperature Range $(T_J)$ | –40°C to + 125°C |

| EN                                 | 0V to 5V         |

**Electrical Characteristics** Limits in standard type are for  $T_J = 25^{\circ}$ C only; limits in **boldface type** apply over the junction temperature ( $T_J$ ) range of -40°C to +125°C. Minimum and Maximum limits are guaranteed through test, design, or statistical correlation. Typical values represent the most likely parametric norm at  $T_J = 25^{\circ}$ C, and are provided for reference purposes only. Unless otherwise stated the following conditions apply:  $V_{IN} = 18V$ .

| Symbol                       | Parameter                                   | Conditions                                                       | Min  | Тур  | Max  | Units |  |

|------------------------------|---------------------------------------------|------------------------------------------------------------------|------|------|------|-------|--|

| Start-Up Regulato            | or, VCC                                     | 4                                                                |      |      |      |       |  |

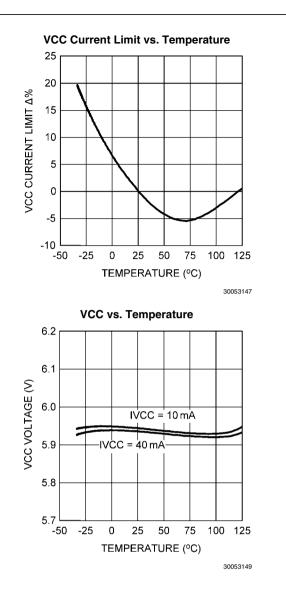

| VCC                          |                                             | $C_{VCC}$ = 1 µF, 0 mA to 40 mA                                  | 5.65 | 5.95 | 6.25 | V     |  |

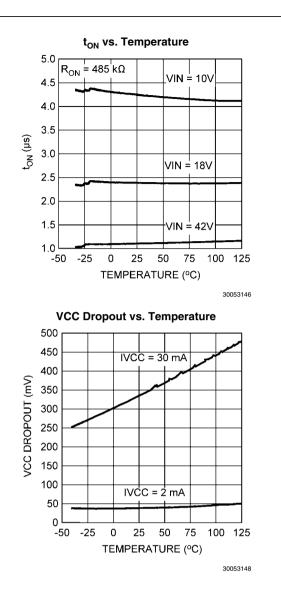

| VIN - VCC                    | VIN - VCC Dropout Voltage                   | $I_{VCC} = 2 \text{ mA}, V_{IN} = 5.5 \text{V}$                  |      | 40   |      | mV    |  |

|                              | VIII - VCC Diopout Voltage                  | $I_{VCC} = 30 \text{ mA}, V_{IN} = 5.5 \text{V}$                 |      | 330  |      |       |  |

| IVCCL                        | VCC Current Limit (Note 3)                  | VCC = 0V                                                         | 65   | 100  |      | mA    |  |

| VCC <sub>UVLO</sub>          | VCC Under-Voltage Lockout Threshold (UVLO)  | VCC Increasing                                                   | 4.75 | 5.1  | 5.40 | v     |  |

| VCC <sub>UVLO-HYS</sub>      | VCC UVLO Hysteresis                         | VCC Decreasing                                                   |      | 475  |      | mV    |  |

| t <sub>CC-UVLO-D</sub>       | VCC UVLO Filter Delay                       |                                                                  |      | 3    |      | μs    |  |

| I <sub>IN</sub>              | Input Operating Current                     | No Switching, V <sub>FB</sub> = 1V                               |      | 3.5  | 5    | mA    |  |

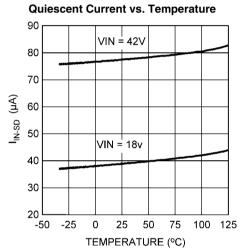

| I <sub>IN-SD</sub>           | Input Operating Current, Device<br>Shutdown | V <sub>EN</sub> = 0V                                             |      | 32   | 55   | μA    |  |

| GATE Drive                   |                                             | •                                                                | -    |      |      |       |  |

| I <sub>Q-BST</sub>           | Boost Pin Leakage                           | $V_{BST} - V_{SW} = 6V$                                          |      | 2    |      | nA    |  |

| R <sub>DS-HG-Pull-Up</sub>   | HG Drive Pull–Up On-Resistance              | I <sub>HG</sub> Source = 200 mA                                  |      | 5    |      | Ω     |  |

| R <sub>DS-HG-Pull-Down</sub> | HG Drive Pull-Down On-Resistance            | I <sub>HG</sub> Sink = 200 mA                                    |      | 3.4  |      | Ω     |  |

| R <sub>DS-LG-Pull-Up</sub>   | LG Drive Pull–Up On-Resistance              | I <sub>LG</sub> Source = 200 mA                                  |      | 3.4  |      | Ω     |  |

| R <sub>DS-LG-Pull-Down</sub> | LG Drive Pull–Down On-Resistance            | I <sub>LG</sub> Sink = 200 mA                                    |      | 2    |      | Ω     |  |

| Soft-Start                   |                                             |                                                                  | 1    |      | 1    |       |  |

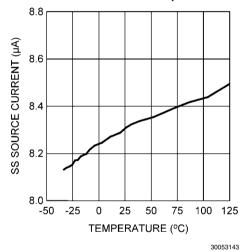

| I <sub>SS</sub>              | SS Pin Source Current                       | V <sub>SS</sub> = 0V                                             | 5.9  | 7.7  | 9.5  | μA    |  |

| I <sub>SS-DIS</sub>          | SS Pin Discharge Current                    |                                                                  |      | 200  |      | μΑ    |  |

| Current Limit                |                                             | ł                                                                | Į    |      | 1    |       |  |

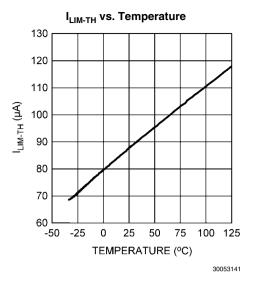

| I <sub>LIM-TH</sub>          | Current Limit Sense Pin Source Current      |                                                                  | 75   | 85   | 95   | μA    |  |

| ON/OFF Timer                 |                                             |                                                                  | 1    |      | 1    | 1 -   |  |

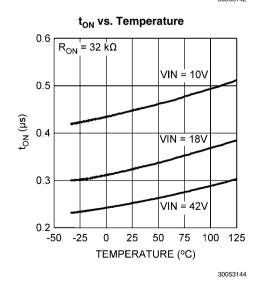

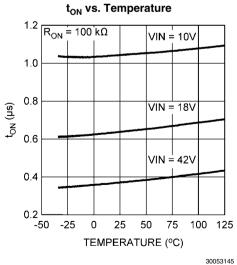

|                              |                                             | $V_{IN} = 10V, R_{ON} = 100 \text{ k}\Omega,$<br>$V_{FB} = 0.6V$ |      | 1.02 |      |       |  |

| t <sub>ON</sub>              | ON Timer Pulse Width                        | $V_{IN} = 18V, R_{ON} = 100 \text{ k}\Omega,$<br>$V_{FB} = 0.6V$ |      | 0.62 |      | μs    |  |

|                              |                                             | $V_{IN} = 42V, R_{ON} = 100 \text{ k}\Omega,$<br>$V_{FB} = 0.6V$ |      | 0.36 |      |       |  |

| t <sub>ON-MIN</sub>          | ON Timer Minimum Pulse Width                | (Note 4)                                                         |      | 200  |      | ns    |  |

| t <sub>OFF</sub>             | OFF Timer Minimum Pulse Width               |                                                                  |      | 370  | 525  | ns    |  |

| Enable Input                 | 1                                           |                                                                  |      |      |      |       |  |

| V <sub>EN</sub>              | EN Pin Input Threshold Trip Point           | V <sub>EN</sub> Rising                                           | 1.14 | 1.20 | 1.26 | V     |  |

| V <sub>EN-HYS</sub>          | EN Pin Threshold Hysteresis                 | V <sub>EN</sub> Falling                                          | 1    | 120  | 1    | mV    |  |

| Symbol             | Parameter                       | Conditions                                                  | Min    | Тур   | Max   | Units  |

|--------------------|---------------------------------|-------------------------------------------------------------|--------|-------|-------|--------|

| Regulation and     | Over-Voltage Comparator         |                                                             |        |       |       |        |

| V <sub>FB</sub>    | In-Regulation Feedback Voltage  | V <sub>SS</sub> > 0.6V                                      | 0.588  | 0.600 | 0.612 | V      |

| V <sub>FB-OV</sub> | Feedback Over-Voltage Threshold |                                                             | 0.690  | 0.720 | 0.748 | V      |

| I <sub>FB</sub>    | Feedback Bias Current           |                                                             |        | 20    |       | nA     |

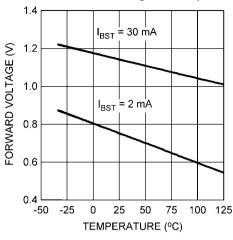

| Boost Diode        | L                               |                                                             |        | •     | •     |        |

|                    | Forward Voltage                 | I <sub>BST</sub> = 2 mA                                     |        | 0.7   |       |        |

| V <sub>f</sub>     |                                 | I <sub>BST</sub> = 30 mA                                    |        | 1     |       | V      |

| Thermal Charac     | teristics                       |                                                             |        |       | •     |        |

| т                  | Thermal Shutdown                | Rising                                                      |        | 165   |       | °C     |

| $T_{SD}$           | Thermal Shutdown Hysteresis     | Falling                                                     |        | 15    |       | °C     |

| 0                  |                                 | 4 Layer JEDEC Printed Circuit<br>Board, 9 Vias, No Air Flow |        | 40    |       |        |

| $\theta_{JA}$      | Junction to Ambient             | 2 Layer JEDEC Printed Circuit<br>Board. No Air Flow         | - 14() |       |       | - °C/W |

| θ <sub>JC</sub>    | Junction to Case                | No Air Flow                                                 |        | 4     |       | °C/W   |

Note 1: Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is intended to be functional, but does not guarantee specific performance limits. For guaranteed specifications and conditions, see the Electrical Characteristics. Note 2: The human body model is a 100 pF capacitor discharged through a 1.5 kΩ resistor into each pin. Test Method is per JESD-22-A114.

Note 2: The numari body model is a 100 pr capacitor discharged through a 1.5 kg resistor into each pin. Test method is per JESD-22-ATT-Note 3: VCC provides self bias for the internal gate drive and control circuits. Device thermal limitations limit external loading.

**Note 4:** See Applications section for minimum on-time when using MOSFETs connected to gate drivers.

# **Typical Performance Characteristics**

Soft-Start Current vs. Temperature

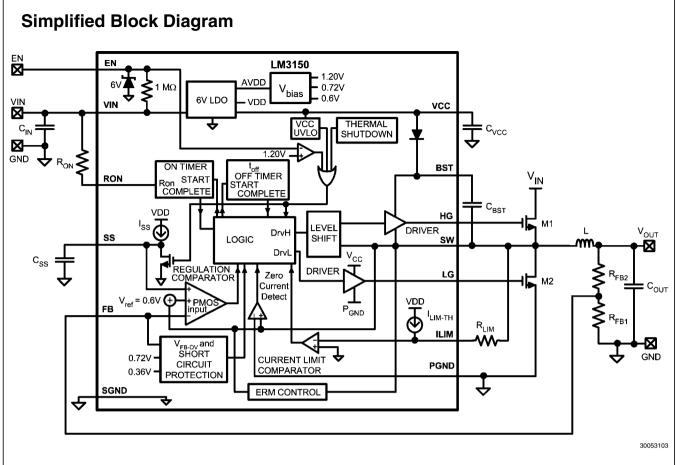

# **Theory of Operation**

The LM3150 synchronous step-down SIMPLE SWITCHER® Controller utilizes a Constant On-Time (COT) architecture which is a derivative of the hysteretic control scheme. COT relies on a fixed switch on-time to regulate the output. The ontime of the high-side switch can be set manually by adjusting the size of an external resistor (R<sub>ON</sub>). To maintain a relatively constant switching frequency as V<sub>IN</sub> varies, the LM3150 automatically adjusts the on-time inversely with the input voltage. Assuming an ideal system and V<sub>IN</sub> is much greater than 1V, the following approximations can be made:

The on-time, t<sub>ON</sub>:

$$t_{ON} = \frac{K \times R_{ON}}{V_{IN}}$$

(1)

(2)

Where constant K = 100 pC

The R<sub>ON</sub> resistance value can be calculated as follows:

$$R_{ON} = \frac{V_{OUT}}{K \times f_{S}}$$

Where f<sub>s</sub> is the desired switching frequency.

Control is based on a comparator and the on-timer, with the output voltage feedback (FB) compared with an internal reference of 0.6V. If the FB level is below the reference, the highside switch is turned on for a fixed time,  $t_{\mbox{\scriptsize ON}},$  which is determined by the input voltage and the resistor R<sub>ON</sub>. Following this on-time, the switch remains off for a minimum off-time,  $t_{\mbox{\scriptsize OFF}}$  , as specified in the Electrical Characteristics table or until the FB pin voltage is below the reference, then the switch turns on again for another on-time period. The switching will continue in this fashion to maintain regulation. During continuous conduction mode (CCM), the switching frequency ideally depends on duty-cycle and on-time only. In a practical application however, there is a small delay in the time that the HG goes low and the SW node goes low that also affects the switching frequency that is accounted for in the typical application curves. The duty-cycle and frequency can be approximated as:

$$D = \frac{t_{ON}}{t_{ON} + t_{OFF}} = t_{ON} \times f_S \approx \frac{V_{OUT}}{V_{IN}}$$

(3)

$$f_{\rm S} = \frac{V_{\rm OUT}}{K \, x \, R_{\rm ON}} \tag{4}$$

Typical COT hysteretic controllers need a significant amount of output capacitor ESR to maintain a minimum amount of ripple at the FB pin in order to switch properly and maintain efficient regulation. The LM3150 however, utilizes a proprietary Emulated Ripple Mode control scheme (ERM) that allows the use of low ESR output capacitors. Not only does this reduce the need for high output capacitor ESR, but also significantly reduces the amount of output voltage ripple seen in a typical hysteretic control scheme. The output ripple voltage can become so low that it is comparable to voltage-mode and current-mode control schemes.

# **Programming the Output Voltage**

The output voltage is set by two external resistors (R\_{FB1},R\_{FB2}). The regulated output voltage is calculated as follows:

$$V_{OUT} = V_{FB} \times \frac{(R_{FB1} + R_{FB2})}{R_{FB1}}$$

(5)

Where  $R_{FB2}$  is the top resistor connected between VOUT and FB, and  $R_{FB1}$  is the bottom resistor connected between FB and GND.

# **Regulation Comparator**

The feedback voltage at FB is compared to the internal reference voltage of 0.6V. In normal operation (the output voltage is regulated), an on-time period is initiated when the voltage at FB falls below 0.6V. The high-side switch stays on for the on-time, causing the FB voltage to rise above 0.6V. After the on-time period, the high-side switch stays off until the FB voltage falls below 0.6V.

## **Over-Voltage Comparator**

The over-voltage comparator is provided to protect the output from over-voltage conditions due to sudden input line voltage changes or output loading changes. The over-voltage comparator continuously monitors the voltage at the FB pin and compares it to a 0.72V internal reference. If the voltage at FB rises above 0.72V, the on-time pulse is immediately terminated. This condition can occur if the input or the output load changes suddenly. Once the over-voltage protection is activated, the HG and LG signals remain off until the voltage at FB pin falls below 0.72V.

# **Current Limit**

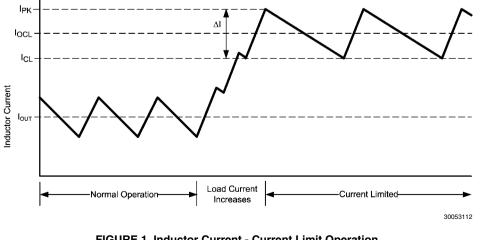

Current limit detection occurs during the off-time by monitoring the current through the low-side switch using an external resistor,  $R_{LIM}$ . If during the off-time the current in the low-side switch exceeds the user defined current limit value, the next on-time cycle is immediately terminated. Current sensing is achieved by comparing the voltage across the low side FET with the voltage across the current limit set resistor  $R_{LIM}$ . If the voltage across  $R_{LIM}$  and the voltage across the low-side FET are equal then the current limit comparator will terminate the next on-time cycle.

The R<sub>LIM</sub> value can be approximated as follows:

$$_{\rm CL} = I_{\rm OCL} - \frac{\Delta I_{\rm L}}{2} \tag{6}$$

$$R_{\text{LIM}} = \frac{I_{\text{CL}} \times R_{\text{DS(ON)max}}}{I_{\text{LIM-TH}}}$$

(7)

Where  $I_{OCL}$  is the user-defined average output current limit value,  $R_{DS(ON)max}$  is the resistance value of the low-side FETat the expected maximum FET junction temperature, and  $I_{LIM-TH}$  is an internal current supply of 85 µA typical.

Figure 1 illustrates the inductor current waveform. During normal operation, the output current ripple is dictated by the switching of the FETs. The current through the low-side switch,  $I_{valley}$ , is sampled at the end of each switching cycle and compared to the current limit,  $I_{CL}$ , current. The valley current can be calculated as follows:

$$I_{\text{valley}} = I_{\text{OUT}} - \frac{\Delta I_{\text{L}}}{2}$$

(8)

Where  $I_{OUT}$  is the average output current and  $\Delta I_{L}$  is the peak-to-peak inductor ripple current.

If an overload condition occurs, the current through the lowside switch will increase which will cause the current limit comparator to trigger the logic to skip the next on-time cycle. The IC will then try to recover by checking the valley current during each off-time. If the valley current is greater than or equal to  $I_{CL}$ , then the IC will keep the low-side FET on and allow the inductor current to further decay.

Throughout the whole process, regardless of the load current, the on-time of the controller will stay constant and thereby the positive ripple current slope will remain constant. During each on-time the current ramps-up an amount equal to:

$$\Delta I_{L} = \frac{(V_{IN} - V_{OUT}) \times t_{ON}}{L}$$

(9)

The valley current limit feature prevents current runaway conditions due to propagation delays or inductor saturation since the inductor current is forced to decay following any overload conditions.

Current sensing is achieved by either a low value sense resistor in series with the low-side FET or by utilizing the R<sub>DS(ON)</sub> of the low-side FET. The R<sub>DS(ON)</sub> sensing method is the preferred choice for a more simplified design and lower costs. The R<sub>DS(ON)</sub> value of a FET has a positive temperature coefficient and will increase in value as the FET's temperature increases. The LM3150 controller will maintain a more stable current limit that is closer to the original value that was set by the user, by positively adjusting the IIIM-TH value as the IC temperature increases. This does not provide an exact temperature compensation but allows for a more tightly controlled current limit when compared to traditional R<sub>DS(ON)</sub> sensing methods when the R<sub>DS(ON)</sub> value can change typically 140% from room to maximum temperature and cause other components to be over-designed. The temperature compensated  $I_{IIM-TH}$  is shown below where  $T_{II}$  is the die temperature of the LM3150 in Celsius:

$$I_{\text{LIM-TH}}(T_{\text{J}}) = I_{\text{LIM-TH}} \times [1 + 3.3 \times 10^{-3} \times (T_{\text{J}} - 27)]$$

(10)

To calculate the  $R_{LIM}$  value with temperature compensation, substitute equation (10) into  $I_{LIM-TH}$  in equation (7).

# **Short-Circuit Protection**

The LM3150 will sense a short-circuit on the output by monitoring the output voltage. When the feedback voltage has fallen below 60% of the reference voltage,  $V_{ref} \times 0.6 ~(\approx 0.36V)$ , short-circuit mode of operation will start. During short-circuit operation, the SS pin is discharged and the output voltage will fall to 0V. The SS pin voltage,  $V_{SS}$ , is then ramped back up at the rate determined by the SS capacitor and  $I_{SS}$  until  $V_{SS}$  reaches 0.7V. During this re-ramp phase, if the short-circuit fault is still present the output current will be equal to the set current limit. Once the soft-start voltage reaches 0.7V the output voltage is sensed again and if the  $V_{FB}$  is still below  $V_{ref} \times 0.6$  then the SS pin is discharged again and the cycle repeats until the short-circuit fault is removed.

# Soft-Start

The soft-start (SS) feature allows the regulator to gradually reach a steady-state operating point, which reduces start-up stresses and current surges. At turn-on, while VCC is below the under-voltage threshold, the SS pin is internally grounded and  $V_{OUT}$  is held at 0V. The SS capacitor is used to slowly ramp  $V_{FB}$  from 0V to 0.6V. By changing the capacitor value, the duration of start-up can be changed accordingly. The start-up time can be calculated using the following equation:

$$t_{SS} = \frac{V_{ref} \times C_{SS}}{I_{SS}}$$

(11)

Where  $t_{SS}$  is measured in seconds,  $V_{ref}$  = 0.6V and  $I_{SS}$  is the soft-start pin source current, which is typically 7.7  $\mu A$  (refer to electrical table).

An internal switch grounds the SS pin if VCC is below the under-voltage lockout threshold, if a thermal shutdown occurs, or if the EN pin is grounded. By using an externally controlled switch, the output voltage can be shut off by grounding the SS pin.

During startup the LM3150 will operate in diode emulation mode, where the low-side gate LG will turn off and remain off when the inductor current falls to zero. Diode emulation mode will allow start-up into a pre-biased output voltage. When softstart is greater than 0.7V, the LM3150 will remain in continuous conduction mode. During diode emulation mode at current limit the low-gate will remain off when the inductor current is off.

FIGURE 1. Inductor Current - Current Limit Operation

-M3150

The soft-start time should be greater than the input voltage rise time and also satisfy the following equality to maintain a smooth transition of the output voltage to the programmed regulation voltage during startup.

$$t_{SS} \ge (V_{OUT} \times C_{OUT}) / (I_{OCL} - I_{OUT})$$

(12)

## Enable/Shutdown

The EN pin can be activated by either leaving the pin floating due to an internal pull up resistor to VIN or by applying a logic high signal to the EN pin of 1.26V or greater. The LM3150 can be remotely shut down by taking the EN pin below 1.02V. Low quiescent shutdown is achieved when  $V_{\rm EN}$  is less than 0.4V. During low quiescent shutdown the internal bias circuitry is turned off.

The LM3150 has certain fault conditions that can trigger shutdown, such as over-voltage protection, current limit, undervoltage lockout, or thermal shutdown. During shutdown, the soft-start capacitor is discharged. Once the fault condition is removed, the soft-start capacitor begins charging, allowing the part to start-up in a controlled fashion. In conditions where there may be an open drain connection to the EN pin, it may be necessary to add a 1 nF bypass capacitor to this pin. This will help decouple noise from the EN pin and prevent false disabling.

# **Thermal Protection**

The LM3150 should be operated such that the junction temperature does not exceed the maximum operating junction temperature. An internal thermal shutdown circuit, which activates at 165°C (typical), takes the controller to a low-power reset state by disabling the buck switch and the on-timer, and grounding the SS pin. This feature helps prevent catastrophic failures from accidental device overheating. When the junction temperature falls back below 150°C the SS pin is released and device operation resumes.

# **Design Guide**

The design guide provides the equations required to design with the LM3150 SIMPLE SWITCHER<sup>®</sup> Controller. WEBENCH<sup>®</sup> design tool can be used with or in place of this section for a more complete and simplified design process.

## 1. Define Power Supply Operating Conditions

- a. Required Output Voltage

- b. Maximum and Minimum DC Input Voltage

- c. Maximum Expected Load Current during Normal Operation d. Soft-Start Time

## 2. Set Output Voltage With Feedback Resistors

$$V_{OUT} = V_{FB} \times \frac{(R_{FB1} + R_{FB2})}{R_{FB1}}$$

(13)

where  $\mathrm{R_{FB1}}$  is the bottom resistor and  $\mathrm{R_{FB2}}$  is the top resistor.

## 3. Determine $R_{ON}$ and $f_s$

The available frequency range for a given input voltage range, is determined by the duty-cycle,  $D = V_{OUT}/V_{IN}$ , and the minimum  $t_{ON}$  and  $t_{OFF}$  times as specified in the electrical characteristics table. The maximum frequency is thus,  $f_{smax} = D_{min}/t_{ON-MIN}$ . Where  $D_{min}=V_{OUT}/V_{IN-MAX}$ , is the minimum duty-cycle. The off-time will need to be less than the minimum off-time  $t_{OFF}$  as specified in the electrical characteristics table plus any turn off and turn on delays of the MOSFETs which can easily add another 200 ns. The minimum desired input voltage. The requirement for minimum off-time is  $t_{OFF} = (1-D_{max})/f_s \ge (t_{OFF})$ . MIN + 200 ns). If  $t_{OFF}$  does not meet this requirement it will be necessary to choose a smaller switching frequency  $f_s$ .

Choose  $R_{ON}$  so that the switching frequency at your typical input voltage matches your  $f_{S}$  chosen above using the following formula:

$$R_{ON} = [(V_{OUT} \times V_{IN}) - V_{OUT}] / (V_{IN} \times K \times f_S) + R_{OND}$$

(14)

$$R_{OND} = -[(V_{IN} - 1) \times (V_{IN} \times 16.5 + 100)] - 1000$$

(15)

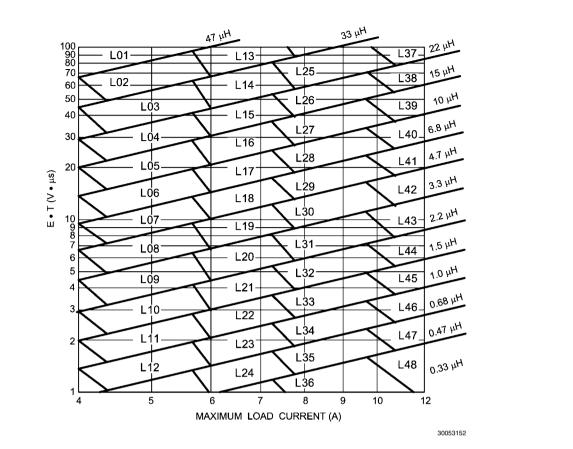

## 4. Determine Inductor Required Using Figure 2

To use the nomograph in *Figure 2*, calculate the inductor voltmicrosecond constant ET from the following formula:

ET = (Vinmax – V<sub>OUT</sub>) x

$$\frac{V_{OUT}}{Vinmax}$$

x  $\frac{1000}{f_s}$  (V x µs) (16)

Where  $f_s$  is in kHz units. The intersection of the Load Current and the Volt-microseconds lines on the chart below will determine which inductors are capable for use in the design. The chart shows a sample of parts that can be used. The offline calculator tools and WEBENCH® will fully calculate the requirements for the components needed for the design.

| FIGURE 2. Inc | uctor Nomograph |

|---------------|-----------------|

|---------------|-----------------|

| TABLE | 1. | Inductor | Selection | Table |

|-------|----|----------|-----------|-------|

|-------|----|----------|-----------|-------|

| Inductor Designator | Inductance<br>(µH) | Current<br>(A) | Part Name         | Vendor    |

|---------------------|--------------------|----------------|-------------------|-----------|

| L01                 | 47                 | 7-9            |                   |           |

| L02                 | 33                 | 7-9            | SER2817H-333KL    | COILCRAFT |

| L03                 | 22                 | 7-9            | SER2814H-223KL    | COILCRAFT |

| L04                 | 15                 | 7-9            | 7447709150        | WURTH     |

| L05                 | 10                 | 7-9            | RLF12560T-100M7R5 | TDK       |

| L06                 | 6.8                | 7-9            | B82477-G4682-M    | EPCOS     |

| L07                 | 4.7                | 7-9            | B82477-G4472-M    | EPCOS     |

| L08                 | 3.3                | 7-9            | DR1050-3R3-R      | COOPER    |

| L09                 | 2.2                | 7-9            | MSS1048-222       | COILCRAFT |

| L10                 | 1.5                | 7-9            | SRU1048-1R5Y      | BOURNS    |

| L11                 | 1                  | 7-9            | DO3316P-102       | COILCRAFT |

| L12                 | 0.68               | 7-9            | DO3316H-681       | COILCRAFT |

| L13                 | 33                 | 9-12           |                   |           |

| L14                 | 22                 | 9-12           | SER2918H-223      | COILCRAFT |

| L15                 | 15                 | 9-12           | SER2814H-153KL    | COILCRAFT |

| L16                 | 10                 | 9-12           | 7447709100        | WURTH     |

| L17                 | 6.8                | 9-12           | SPT50H-652        | COILCRAFT |

| L18                 | 4.7                | 9-12           | SER1360-472       | COILCRAFT |

| L19                 | 3.3                | 9-12           | MSS1260-332       | COILCRAFT |

| L20                 | 2.2                | 9-12           | DR1050-2R2-R      | COOPER    |

## www.national.com

LM3150

| nductor Designator | Inductance<br>(μH) | Current<br>(A) | Part Name      | Vendor    |

|--------------------|--------------------|----------------|----------------|-----------|

| L21                | 1.5                | 9-12           | DR1050-1R5-R   | COOPER    |

| L22                | 1                  | 9-12           | DO3316H-102    | COILCRAFT |

| L23                | 0.68               | 9-12           |                |           |

| L24                | 0.47               | 9-12           |                |           |

| L25                | 22                 | 12-15          | SER2817H-223KL | COILCRAFT |

| L26                | 15                 | 12-15          |                |           |

| L27                | 10                 | 12-15          | SER2814L-103KL | COILCRAFT |

| L28                | 6.8                | 12-15          | 7447709006     | WURTH     |

| L29                | 4.7                | 12-15          | 7447709004     | WURTH     |

| L30                | 3.3                | 12-15          |                |           |

| L31                | 2.2                | 12-15          |                |           |

| L32                | 1.5                | 12-15          | MLC1245-152    | COILCRAFT |

| L33                | 1                  | 12-15          |                |           |

| L34                | 0.68               | 12-15          | DO3316H-681    | COILCRAFT |

| L35                | 0.47               | 12-15          |                |           |

| L36                | 0.33               | 12-15          | DR73-R33-R     | COOPER    |

| L37                | 22                 | 15-            |                |           |

| L38                | 15                 | 15-            | SER2817H-153KL | COILCRAFT |

| L39                | 10                 | 15-            | SER2814H-103KL | COILCRAFT |

| L40                | 6.8                | 15-            |                |           |

| L41                | 4.7                | 15-            | SER2013-472ML  | COILCRAFT |

| L42                | 3.3                | 15-            | SER2013-362L   | COILCRAFT |

| L43                | 2.2                | 15-            |                |           |

| L44                | 1.5                | 15-            | HA3778–AL      | COILCRAFT |

| L45                | 1                  | 15-            | B82477-G4102-M | EPCOS     |

| L46                | 0.68               | 15-            |                |           |

| L47                | 0.47               | 15-            |                |           |

| L48                | 0.33               | 15-            |                |           |

## 5. Determine Output Capacitance

Typical hysteretic COT converters similar to the LM3150 require a certain amount of ripple that is generated across the ESR of the output capacitor and fed back to the error comparator. Emulated Ripple Mode control built into the LM3150 will recreate a similar ripple signal and thus the requirement for output capacitor ESR will decrease compared to a typical Hysteretic COT converter. The emulated ripple is generated by sensing the voltage signal across the low-side FET and is then compared to the FB voltage at the error comparator input to determine when to initiate the next on-time period.

$$C_{Omin} = 70 / (f_s^2 x L)$$

(17)

The maximum ESR allowed to prevent over-voltage protection during normal operation is:

$$ESR_{max} = (80 \text{ mV x L x A}_{f}) / ET_{min}$$

(18)

$\text{ET}_{\text{min}}$  is calculated using  $\text{V}_{\text{IN-MIN}}$

$A_f = V_{OUT} / 0.6$  if there is no feed-forward capacitor used

A<sub>f</sub> = 1 if there is a feed-forward capacitor used

The minimum ESR must meet both of the following criteria:

$$\text{ESR}_{\min} \ge (15 \text{ mV x L x A}_{f}) / \text{ET}_{\max}$$

(19)

$$\mathsf{ESR}_{\mathsf{min}} \ge [\mathsf{ET}_{\mathsf{max}} / (\mathsf{V}_{\mathsf{IN}} - \mathsf{V}_{\mathsf{OUT}})] \times (\mathsf{A}_{\mathsf{f}} / \mathsf{C}_{\mathsf{O}}) \tag{20}$$

$ET_{max}$  is calculated using  $V_{IN-MAX}$ .

Any additional parallel capacitors should be chosen so that their effective impedance will not negatively attenuate the output ripple voltage.

### 6. Determine The Use of Feed-Forward Capacitor

Certain applications may require a feed-forward capacitor for improved stability and easier selection of available output capacitance. Use the following equation to calculate the value of  $C_{\rm ff}$ .

$$Z_{FB} = (R_{FB1} \times R_{FB2}) / (R_{FB1} + R_{FB2})$$

(21)

$$C_{\rm ff} = V_{\rm OUT} / (V_{\rm IN-MIN} \times f_{\rm S} \times Z_{\rm FB})$$

(22)

## 7. MOSFET and R<sub>LIM</sub> Selection

The high-side and low-side FETs must have a drain to source  $(V_{DS})$  rating of at least 1.2 x  $V_{IN}.$

Use the following equations to calculate the desired target value of the low-side FET  $R_{DS(ON)}$  for current limit.

$$\mathsf{R}_{\mathsf{LIM}}\left(\mathsf{T}_{j}\right) = \frac{\mathsf{I}_{\mathsf{CL}} \times \mathsf{R}_{\mathsf{DS}(\mathsf{ON})\mathsf{max}}}{\mathsf{I}_{\mathsf{LIM-TH}}\left(\mathsf{T}_{j}\right)} \tag{23}$$

$$I_{\text{LIM-TH}}(T_{i}) = I_{\text{LIM-TH}} \times [1 + 3.3 \times 10^{-3} \times (T_{i} - 27)]$$

(24)

The gate drive current from VCC must not exceed the minimum current limit of VCC. The drive current from VCC can be calculated with:

$$I_{VCCdrive} = Q_{gtotal} \times f_{S}$$

(25)

Where,  $\mathbf{Q}_{\text{gtotal}}$  is the combined total gate charge of the high-side and low-side FETs.

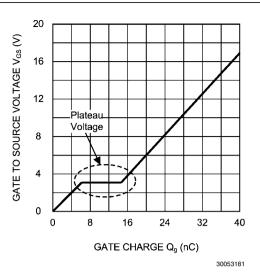

The plateau voltage of the FET  $V_{GS}$  vs  $Q_g$  curve, as shown in Figure 3, must be less than VCC - 750 mV.

FIGURE 3. Typical MOSFET Gate Charge Curve

See following design example for estimated power dissipation calculation.

### 8. Calculate Input Capacitance

The main parameters for the input capacitor are the voltage rating, which must be greater than or equal to the maximum DC input voltage of the power supply, and its rms current rating. The maximum rms current is approximately 50% of the maximum load current.

$$C_{IN} = \frac{Iomax x D x (1-D)}{f_s x \Delta V_{IN-MAX}}$$

(26)

Where,  $\Delta V_{\text{IN-MAX}}$  is the maximum allowable input ripple voltage. A good starting point for the input ripple voltage is 5% of  $V_{\text{IN}}$

When using low ESR ceramic capacitors on the input of the LM3150 a resonant circuit can be formed with the impedance of the input power supply and parasitic impedance of long leads/PCB traces to the LM3150 input capacitors. It is recommended to use a damping capacitor under these circumstances, such as aluminum electrolytic that will prevent ringing on the input. The damping capacitor should be chosen to be approximately 5 times greater than the parallel ceramic capacitors combination. The total input capacitance should be greater than 10 times the input inductance of the power supply leads/pcb trace. The damping capacitor should also be chosen to handle its share of the rms input current which is shared proportionately with the parallel impedance of the ceramic capacitors and aluminum electrolytic at the LM3150 switching frequency.

The  $C_{\text{BYP}}$  capacitor should be placed directly at the VIN pin. The recommended value is 0.1  $\mu\text{F}.$

### 9. Calculate Soft-Start Capacitor

С

$$_{\rm SS} = \frac{I_{\rm SS} \times I_{\rm SS}}{V_{\rm ref}}$$

(27)

Where  $t_{ss}$  is the soft-start time in seconds and  $V_{ref} = 0.6V$ .

### 10. $C_{VCC}$ , $C_{BST}$ and $C_{EN}$

$C_{VCC}$  should be placed directly at the VCC pin with a recommended value of 1  $\mu F$  to 2.2  $\mu F.$  For input voltage ranges that include voltages below 8V a 1  $\mu F$  capacitor must be used for  $C_{VCC}.$   $C_{BST}$  creates a voltage used to drive the gate of the

high-side FET. It is charged during the SW off-time. The recommended value for  $C_{\rm BST}$  is 0.47  $\mu F.$  The EN bypass capac-

itor,  $\rm C_{EN},$  recommended value is 1000 pF when driving the EN pin from open drain type of signal.

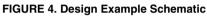

# **Design Example**

1. Define Power Supply Operating Conditions

a. V<sub>OUT</sub> = 3.3V

- b.  $V_{\text{IN-MIN}} = 6V$ ,  $V_{\text{IN-TYP}} = 12V$ ,  $V_{\text{IN-MAX}} = 24V$

- c. Typical Load Current = 12A, Max Load Current = 15A

- d. Soft-Start time  $t_{SS} = 5 \text{ ms}$

- 2. Set Output Voltage with Feedback Resistors

$$\mathsf{R}_{\mathsf{FB2}} = \mathsf{R}_{\mathsf{FB1}} \left( \frac{\mathsf{V}_{\mathsf{OUT}}}{\mathsf{V}_{\mathsf{FB}}} - 1 \right)$$

$$R_{FB2} = 4.99 \text{ k}\Omega \left(\frac{3.3 \text{V}}{0.6 \text{V}} - 1\right)$$

$R_{FB2} = 22.455 \text{ k}\Omega$

$R_{FB2}$  = 22.6 k $\Omega$ , nearest 1% standard value.

3. Determine  $\rm R_{ON}$  and  $\rm f_{S}$

t,

$$\begin{split} D_{min} &= V_{OUT}/V_{IN-MAX} \\ D_{min} &= 3.3V/24V = 0.137 \\ D_{max} &= 3.3V / 6V = 0.55 \\ \hline s_{max} &= 0.137 / 200 \text{ ns} = 687 \text{ kHz} \\ D_{max} &= V_{OUT}/V_{IN-MIN} \\ D_{FF} &= (1-0.55)/687 \text{ kHz} = 654 \text{ ns} \end{split}$$

$\ensuremath{t_{\text{OFF}}}$  should meet the following criteria:

$$t_{OFF} > t_{OFF-MIN} + 200 \text{ ns}$$

$t_{OFF} > 725 \text{ ns}$

At the maximum switching frequency of 687 kHz, which is limited by the minimum on-time, the off-time of 654 ns is less than 725 ns. Therefore the switching frequency should be reduced and meet the following criteria:

f<sub>s</sub> < (1 - D)/725 ns

A switching frequency is arbitrarily chosen at 500 kHz which should allow for reasonable size components and satisfies the requirements above.

Using  $f_s = 500$  kHz  $R_{ON}$  can be calculated as follows:

$$\begin{aligned} \mathsf{R}_{\mathsf{ON}} &= [(\mathsf{V}_{\mathsf{OUT}} \times \mathsf{V}_{\mathsf{IN}}) - \mathsf{V}_{\mathsf{OUT}}] / (\mathsf{V}_{\mathsf{IN}} \times \mathsf{K} \times \mathsf{f}_{\mathsf{S}}) + \mathsf{R}_{\mathsf{OND}} \\ \mathsf{R}_{\mathsf{OND}} &= - [(\mathsf{V}_{\mathsf{IN}} - 1) \times (\mathsf{V}_{\mathsf{IN}} \times 16.5 + 100)] - 1000 \end{aligned}$$

$$R_{OND} = -[(12 - 1) \times (12 \times 16.5 + 100)] -1000$$

$R_{OND} = -4.3 \text{ k}\Omega$

$R_{ON} = [(3.3 \text{ x } 12) - 3.3] / (12 \text{ x } 100 \text{ pC } \text{ x } 500 \text{ kHz}) - 4.3 \text{ k}\Omega$

$$R_{ON} = 56.2 \text{ k}\Omega$$

## 4. Determine Inductor Required

a. ET = (24-3.3) x (3.3/24) x (1000/500) = 5.7 V µs

b. From the inductor nomograph a 12A load and 5.7 V  $\mu$ s calculation corresponds to a L44 type of inductor.

c. Using the inductor designator L44 in *Table 1* the Coilcraft HA3778–AL 1.65  $\mu$ H inductor is chosen.

## 5. Determine Output Capacitance

The voltage rating on the output capacitor should be greater than or equal to the output voltage. As a rule of thumb most capacitor manufacturers suggests not to exceed 90% of the capacitor rated voltage. In the case of multilayer ceramics the capacitance will tend to decrease dramatically as the applied voltage is increased towards the capacitor rated voltage. The capacitance can decrease by as much as 50% when the applied voltage is only 30% of the rated voltage. The chosen capacitor should also be able to handle the rms current which is equal to:

Irmsco = I<sub>OUT</sub> x

$$\frac{r}{\sqrt{12}}$$

For this design the chosen ripple current ratio, r = 0.3, represents the ratio of inductor peak-to-peak current to load current IOUT. A good starting point for ripple ratio is 0.3 but it is acceptable to choose r between 0.25 to 0.5. The nomographs in this datasheet all use 0.3 as the ripple current ratio.

Irmsco =

$$12 \times \frac{0.3}{\sqrt{12}}$$

I<sub>rmsco</sub> = 1A

Minimum output capacitance is:

$$C_{Omin} = 70 / (f_s^2 \times L)$$

$$C_{Omin} = 70 / (500 \text{ kHz}^2 \text{ x } 1.65 \text{ }\mu\text{H}) = 169 \text{ }\mu\text{F}$$

The maximum ESR allowed to prevent over-voltage protection during normal operation is:

$\text{ESR}_{\text{max}} = (80 \text{ mV x L x A}_{\text{f}}) / \text{ET}$

$A_f = V_{OUT} / 0.6$  without a feed-forward capacitor

$A_f = 1$  with a feed-forward capacitor

For this design a feed-forward capacitor will be used to help minimize output ripple.

ESR<sub>max</sub> = (80 mV x 1.65 µH x 1) / 5.7 V µs

$$\text{ESR}_{\text{max}} = 23 \text{ m}\Omega$$

The minimum ESR must meet both of the following criteria:

$\text{ESR}_{\text{min}} \ge (15 \text{ mV x L x A}_{\text{f}}) / \text{ET}$

$\text{ESR}_{\text{min}} \ge [\text{ ET } / (\text{V}_{\text{IN}} - \text{V}_{\text{OUT}})] \times (\text{A}_{\text{f}} / \text{C}_{\text{O}})$

ESR<sub>min</sub> ≥ (15 mV x 1.65 μH x 1) / 5.7 V μs = 4.3 mΩ

$\text{ESR}_{\text{min}} \ge [5.7 \text{ V} \ \mu\text{s} \ / \ (12 - 3.3) \ ] \ \text{x} \ (1 \ / \ 169 \ \mu\text{F}) = 3.9 \ \text{m}\Omega$

Based on the above criteria two 150 µF polymer aluminum capacitors with a ESR = 12 m $\Omega$  each for a effective ESR in parallel of 6 m $\Omega$  was chosen from Panasonic. The part number is EEF-UE0J101P.

## 6. Determine Use of Feed-Forward Capacitor

From step 5 the capacitor chosen in ESR is small enough that we should use a feed-forward capacitor. This is calculated from:

$$C_{\rm ff} = \frac{V_{\rm OUT}}{V_{\rm IN-MIN} \times f_{\rm s}} \times \frac{R_{\rm FB1} + R_{\rm FB2}}{R_{\rm FB1} \times R_{\rm FB2}}$$

$$C_{\rm ff} = \frac{3.3V}{\Omega \times f_{\rm s}} \times \frac{4.99 \,\text{k}\Omega + 22.6 \,\text{k}\Omega}{\Omega \times f_{\rm s}} = 269$$

$$\Sigma_{\rm ff} = \frac{3.3 \text{V}}{6 \text{V} \times 500 \text{ kHz}} \times \frac{4.99 \text{ k}\Omega + 22.6 \text{ k}\Omega}{4.99 \text{ k}\Omega \times 22.6 \text{ k}\Omega} = 269 \text{ pF}$$

Let  $C_{ff}$  = 270 pF, which is the closest next standard value.

### 7. MOSFET and RLIM Selection

The LM3150 is designed to drive N-channel MOSFETs. For a maximum input voltage of 24V we should choose N-channel MOSFETs with a maximum drain-source voltage, V<sub>DS</sub>, greater than 1.2 x 24V = 28.8V. FETs with maximum  $V_{DS}$  of 30V will be the first option. The combined total gate charge  $\mathbf{Q}_{\text{qtotal}}$  of the high-side and low-side FET should satisfy the following:

$$Q_{gtotal} \leq I_{VCCL} / f_s$$

$$Q_{\text{ototal}} \le 65 \text{ mA} / 500 \text{ kHz}$$

Q<sub>atotal</sub> ≤ 130 nC

Where  $I_{\mbox{VCCL}}$  is the minimum current limit of VCC, over the temperature range, specified in the electrical characteristics table. The MOSFET gate charge Q<sub>n</sub> is gathered from reading the V<sub>GS</sub> vs Q<sub>a</sub> curve of the MOSFET datasheet at the V<sub>GS</sub> = 5V for the high-side, M1, MOSFET and  $V_{GS} = 6V$  for the lowside, M2, MOSFET.

The Renesas MOSFET RJK0305DPB has a gate charge of 10 nC at  $V_{GS}$  = 5V, and 12 nC at  $V_{GS}$  = 6V. This combined gate charge for a high-side, M1, and low-side, M2, MOSFET 12 nC + 10 nC = 22 nC is less than 130 nC calculated Q<sub>qtotal</sub>.

The calculated MOSFET power dissipation must be less than the max allowed power dissipation, Pdmax, as specified in the MOSFET datasheet. An approximate calculation of the FET power dissipated Pd, of the high-side and low-side FET is given by:

### **High-Side MOSFET**

Pcond =

$$I_{out}^2 \times R_{DS(ON)} \times D$$

Psw =  $\frac{1}{2} \times V_{in} \times I_{out} \times Q_{gd} \times f_s \times \left(\frac{8.5}{Vcc - Vth} + \frac{6.8}{Vth}\right)$

Pdh = Pcond + Psw

Pcond = 12<sup>2</sup> x 0.01 x 0.275 = 0.396W

$$P_{SW} = \frac{1}{2} \times 12 \times 12 \times 1.5 \text{ nC} \times 500 \text{ kHz} \times \left(\frac{8.5}{6-2.5} + \frac{6.8}{2.5}\right) = 0.278W$$

Pdh = 0.396 + 0.278 = 0.674W

The max power dissipation of the RJK0305DPB is rated as 45W for a junction temperature that is 125°C higher than the case temperature and a thermal resistance from the FET junction to case,  $\theta_{JC}$ , of 2.78°C/W. When the FET is mounted onto the PCB, the PCB will have some additional thermal resistance such that the total system thermal resistance of the FET package and the PCB,  $\theta_{JA}$ , is typically in the range of 30° C/W for this type of FET package. The max power dissipation, Pdmax, with the FET mounted onto a PCB with a 125°C junction temperature rise above ambient temperature and  $\theta_{JA}$  = 30°C/W, can be estimated by:

The system calculated Pdh of 0.674W is much less than the FET Pdmax of 4.1W and therefore the RJK0305DPB max allowable power dissipation criteria is met.

## Low-Side MOSFET

Primary loss is conduction loss given by:

PdI = Iout<sup>2</sup> x R<sub>DS(ON)</sub> x (1-D) = 122 x 0.01 x (1-0.275) = 1W

Pdl is also less than the Pdmax specified on the RJK0305DPB MOSFET datasheet.

However, it is not always necessary to use the same MOS-FET for both the high-side and low-side. For most applications it is necessary to choose the high-side MOSFET with the lowest gate charge and the low-side MOSFET is chosen for the lowest allowed R<sub>DS(ON)</sub>. The plateau voltage of the FET V<sub>GS</sub> vs Q<sub>g</sub> curve must be less than VCC - 750 mV.

The current limit resistor, R<sub>LIM</sub>, is calculated by estimating the R<sub>DS(ON)</sub> of the low-side FET at the maximum junction temperature of 100°C. By choosing to go into current limit when the average output load current is 20% higher than the output load current of 12A while the inductor ripple current ratio is 1/3 of the load current will make I<sub>CL</sub>= 10.4A. Then the following calculation of R<sub>LIM</sub> is:

$R_{IIM} = (10.4 \times 0.014) / (75 \times 10^{-6}) = 1.9 \text{ k}\Omega$

Let  $R_{LIM} = 1.91 \text{ k}\Omega$  which is the next standard value.

### 8. Calculate Input Capacitance

The input capacitor should be chosen so that the voltage rating is greater than the maximum input voltage which for this example is 24V. Similar to the output capacitor, the voltage rating needed will depend on the type of capacitor chosen. The input capacitor should also be able to handle the input rms current, which is a maximum of approximately 0.5 x  $I_{OUT}$ . For this example the rms input current is approximately 0.5 x 12A = 6A.

The minimum capacitance with a maximum 5% input ripple  $\Delta V_{IN-MAX} = (0.05 \text{ x } 12) = 0.6 \text{V}$ :

C<sub>IN</sub> = [12 x 0.275 x (1-0.275)] / [500 kHz x 0.6] = 8 μF

To handle the large input rms current 2 ceramic capacitors are chosen at 10  $\mu$ F each with a voltage rating of 50V and case size of 1210. Each ceramic capacitor is capable of handling 3A of rms current. A aluminum electrolytic of 5 times the combined input capacitance, 5 x 20  $\mu$ F = 100  $\mu$ F, is chosen to provide input voltage filter damping because of the low ESR ceramic input capacitors.

$C_{\text{BYP}}$  = 0.1 $\mu F$  ceramic with a voltage rating greater than maximum  $V_{\text{IN}}$

#### 9. Calculate Soft-Start Capacitor

The soft start-time should be greater than the input voltage rise time and also satisfy the following equality to maintain a smooth transition of the output voltage to the programmed regulation voltage during startup. The desired soft-start time, tss, of 5 ms also needs to satisfy the equality in equation 12, by using the chosen component values through the previous steps as shown below:

$5 \text{ ms} > (3.3 \text{V x} 300 \ \mu\text{F}) / (1.2 \text{ x} 12 \text{A} - 12 \text{A})$

#### 5 ms > 0.412 ms

Since the desired soft-start time satisfies the equality in equation 12, the soft start capacitor is calculated as:

$$C_{SS} = (7.7 \ \mu A \ x \ 5 \ ms) / 0.6V = 0.064 \ \mu F$$

Let  $C_{SS} = 0.068 \ \mu$ F, which is the next closest standard value. This should be a ceramic cap with a voltage rating greater than 10V.

## 10. C<sub>VCC</sub>, C<sub>EN</sub>, and C<sub>BST</sub>

$C_{VCC} = 1 \ \mu F$  ceramic with a voltage rating greater than 10V  $C_{EN} = 1000 \ pF$  ceramic with a voltage rating greater than 10V  $C_{BST} = 0.47 \ \mu F$  ceramic with a voltage rating greater than 10V

| Bill of Mat                           | terials  |                                       |                        |                    |

|---------------------------------------|----------|---------------------------------------|------------------------|--------------------|

| Designator                            | Value    | Parameters                            | Manufacturer           | Part Number        |

| C <sub>BST</sub>                      | 0.47 µF  | Ceramic, X7R, 16V, 10%                | TDK                    | C2012X7R1C474K     |

| C <sub>BYP</sub>                      | 0.1 µF   | Ceramic, X7R, 50V, 10%                | TDK                    | C2012X7R1H104K     |

| C <sub>EN</sub>                       | 1000 pF  | Ceramic, X7R, 50V, 10%                | TDK                    | C1608X7R1H102K     |

| C <sub>FF</sub>                       | 270 pF   | Ceramic, C0G, 50V, 5%                 | Vishay-Bccomponents    | VJ0805A271JXACW1BC |

| C <sub>IN1</sub> , C <sub>IN2</sub>   | 10 µF    | Ceramic, X5R, 35V, 20%                | Taiyo Yuden            | GMK325BJ106KN-T    |

| C <sub>OUT1</sub> , C <sub>OUT2</sub> | 150 µF   | Polymer Aluminum, , 6.3V, 20%         | Panasonic              | EEF-UE0J151R       |

| C <sub>SS</sub>                       | 0.068 µF | Ceramic, 0805, 25V, 10%               | Vishay                 | VJ0805Y683KXXA     |

| C <sub>VCC</sub>                      | 1 µF     | Ceramic, X7R, 16V, 10%                | Kemet                  | C0805C105K4RACTU   |

| L1                                    | 1.65 µH  | Shielded Drum Core, 2.53 m $\Omega$   | Coilcraft              | HA3778–AL          |

| M1, M2                                | 30V      | 8 nC, R <sub>DS(ON)</sub> @4.5V=10 mΩ | Renesas                | RJK0305DPB         |

| R <sub>FB1</sub>                      | 4.99 kΩ  | 1%, 0.125W                            | Vishay-Dale            | CRCW08054k99FKEA   |

| R <sub>FB2</sub>                      | 22.6 kΩ  | 1%, 0.125W                            | Vishay-Dale            | CRCW080522k6FKEA   |

| R <sub>LIM</sub>                      | 1.91 kΩ  | 1%, 0.125W                            | Vishay-Dale            | CRCW08051K91FKEA   |

| R <sub>ON</sub>                       | 56.2 kΩ  | 1%, 0.125W                            | Vishay-Dale            | CRCW080556K2FKEA   |

| U1                                    | LM3150   |                                       | National Semiconductor | LM3150MH           |

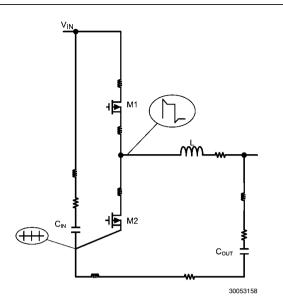

# **PCB Layout Considerations**

It is good practice to layout the power components first, such as the input and output capacitors, FETs, and inductor. The first priority is to make the loop between the input capacitors and the source of the low-side FET to be very small and tie the grounds of the low-side FET and input capacitor directly to each other and then to the ground plane through vias. As shown in *Figure 5* when the input capacitor ground is tied directly to the source of the low-side FET, parasitic inductance in the power path, along with noise coupled into the ground plane, are reduced.

The switch node is the next item of importance. The switch node should be made only as large as required to handle the load current. There are fast voltage transitions occurring in the switch node at a high frequency, and if the switch node is made too large it may act as an antennae and couple switching noise into other parts of the circuit. For high power designs, it is recommended to use a multi-laver board. The FETs are going to be the largest heat generating devices in the design, and as such, care should be taken to remove the heat. On multi-layer boards using exposed-pad packages for the FETs such as the power-pak SO-8, vias should be used under the FETs to the same plane on the interior layers to help dissipate the heat and cool the FETs. For the typical single FET Power-Pak type FETs, the high-side FET DAP is  $V_{IN}$ . The V<sub>IN</sub> plane should be copied to the other interior layers to the bottom layer for maximum heat dissipation. Likewise, the DAP of the low-side FET is connected to the SW node and the SW node shape should be duplicated to the other PCB layers for maximum heat dissipation.

See the Evaluation Board application note AN-1900 for an example of a typical multi-layer board layout, and the Demonstration Board Reference Design Application Note for a typical 2 layer board layout. Each design allows for single sided component mounting.

FIGURE 6. PCB Placement of Power Stage

# Notes

For more National Semiconductor product information and proven design tools, visit the following Web sites at:

| Pr                             | oducts                       | De                      | esign Support                  |

|--------------------------------|------------------------------|-------------------------|--------------------------------|

| Amplifiers                     | www.national.com/amplifiers  | WEBENCH                 | www.national.com/webench       |

| Audio                          | www.national.com/audio       | Analog University       | www.national.com/AU            |

| Clock Conditioners             | www.national.com/timing      | App Notes               | www.national.com/appnotes      |

| Data Converters                | www.national.com/adc         | Distributors            | www.national.com/contacts      |

| Displays                       | www.national.com/displays    | Green Compliance        | www.national.com/quality/green |

| Ethernet                       | www.national.com/ethernet    | Packaging               | www.national.com/packaging     |

| Interface                      | www.national.com/interface   | Quality and Reliability | www.national.com/quality       |

| LVDS                           | www.national.com/lvds        | Reference Designs       | www.national.com/refdesigns    |

| Power Management               | www.national.com/power       | Feedback                | www.national.com/feedback      |

| Switching Regulators           | www.national.com/switchers   |                         |                                |

| LDOs                           | www.national.com/ldo         |                         |                                |

| LED Lighting                   | www.national.com/led         |                         |                                |

| PowerWise                      | www.national.com/powerwise   |                         |                                |

| Serial Digital Interface (SDI) | www.national.com/sdi         |                         |                                |

| Temperature Sensors            | www.national.com/tempsensors |                         |                                |

| Wireless (PLL/VCO)             | www.national.com/wireless    |                         |                                |

THE CONTENTS OF THIS DOCUMENT ARE PROVIDED IN CONNECTION WITH NATIONAL SEMICONDUCTOR CORPORATION ("NATIONAL") PRODUCTS. NATIONAL MAKES NO REPRESENTATIONS OR WARRANTIES WITH RESPECT TO THE ACCURACY OR COMPLETENESS OF THE CONTENTS OF THIS PUBLICATION AND RESERVES THE RIGHT TO MAKE CHANGES TO SPECIFICATIONS AND PRODUCT DESCRIPTIONS AT ANY TIME WITHOUT NOTICE. NO LICENSE, WHETHER EXPRESS, IMPLIED, ARISING BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT.

TESTING AND OTHER QUALITY CONTROLS ARE USED TO THE EXTENT NATIONAL DEEMS NECESSARY TO SUPPORT NATIONAL'S PRODUCT WARRANTY. EXCEPT WHERE MANDATED BY GOVERNMENT REQUIREMENTS, TESTING OF ALL PARAMETERS OF EACH PRODUCT IS NOT NECESSARILY PERFORMED. NATIONAL ASSUMES NO LIABILITY FOR APPLICATIONS ASSISTANCE OR BUYER PRODUCT DESIGN. BUYERS ARE RESPONSIBLE FOR THEIR PRODUCTS AND APPLICATIONS USING NATIONAL COMPONENTS. PRIOR TO USING OR DISTRIBUTING ANY PRODUCTS THAT INCLUDE NATIONAL COMPONENTS, BUYERS SHOULD PROVIDE ADEQUATE DESIGN, TESTING AND OPERATING SAFEGUARDS.

EXCEPT AS PROVIDED IN NATIONAL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, NATIONAL ASSUMES NO LIABILITY WHATSOEVER, AND NATIONAL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY RELATING TO THE SALE AND/OR USE OF NATIONAL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

## LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS PRIOR WRITTEN APPROVAL OF THE CHIEF EXECUTIVE OFFICER AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

Life support devices or systems are devices which (a) are intended for surgical implant into the body, or (b) support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in a significant injury to the user. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system or to affect its safety or effectiveness.

National Semiconductor and the National Semiconductor logo are registered trademarks of National Semiconductor Corporation. All other brand or product names may be trademarks or registered trademarks of their respective holders.

### Copyright© 2008 National Semiconductor Corporation

For the most current product information visit us at www.national.com

National Semiconductor Americas Technical Support Center Email: support@nsc.com Tel: 1-800-272-9959 National Semiconductor Europe Technical Support Center Email: europe.support@nsc.com German Tel: +49 (0) 180 5010 771 English Tel: +44 (0) 870 850 4288 National Semiconductor Asia Pacific Technical Support Center Email: ap.support@nsc.com National Semiconductor Japan Technical Support Center Email: jpn.feedback@nsc.com